Top Headlines

Articles11 months ago

Why Some NAND Gates Behave Differently: Subtle Effects at the Silicon Level

NAND gates are fundamental building blocks in digital electronics, often regarded as the universal gate because of their ability to implement any logical function. Typically, their behavior is well-understood and predictable, derived from the principles of Boolean algebra and semiconductor physics. However, when delving into the silicon level, certain subtle effects can cause some NAND gates to behave unexpectedly or differently from their idealized models. These variations may surprise practitioners and can be critical considerations in high-precision or high-speed applications. At the most basic level, NAND gates are constructed from transistors—either MOSFETs in CMOS technology or BJTs in older designs. In CMOS structures, the gates involve a complementary pair of p-type and n-type MOSFETs. When the input signals change state, the current path through these transistors switches, producing the desired logic output. Ideally, this switching process occurs instantly; in practice, several subtle physical effects influence the actual timing, power consumption, and even the logic threshold levels. One factor leading to different behaviors is the variability inherent in silicon fabrication. Manufacturing processes can introduce tiny differences in transistor dimensions, doping concentrations, and oxide thicknesses, all of which influence the threshold voltage (Vth) of individual transistors. Such variations can cause some NAND gates to switch at slightly different input voltages or exhibit asymmetric rise and fall times, affecting circuit timing and potentially causing logic errors in tightly synchronized systems. Another subtle effect involves leakage currents. Although CMOS transistors are designed to minimize current flow when off, in reality, small leakage paths exist. These leakage currents are sensitive to temperature fluctuations, supply voltage variations, and manufacturing imperfections. In some cases, they can cause marginally different gate behaviors, especially at low supply voltages or very high speeds, where the leaky transistors might inadvertently switch states or delay switching. Parasitic capacitances and inductances also come into play at the silicon level. Even tiny parasitic elements associated with transistor junctions, interconnects, and the overall circuit layout can influence the speed and stability of NAND gates. These effects are often more pronounced at higher frequencies, where the inductive and capacitive elements introduce phase shifts and potential signal integrity issues, leading to behaviors deviating from the ideal digital switching profiles. Temperature effects are equally significant. As the chip heats up during operation, semiconductor properties shift—threshold voltages decrease or increase, carrier mobility changes, and leakage currents can spike. These shifts can temporarily alter the behavior of certain NAND gates, causing timing skew or voltage level variations. Such temperature-dependent behavior can be particularly problematic in environments with fluctuating conditions, like outdoor electronics or high-performance computing systems. Moreover, aging phenomena such as bias temperature instability (BTI) and hot-carrier injection gradually alter the transistor characteristics over time. These changes can lead to slow drifts in the threshold voltage, intermittently causing some NAND gates to behave differently than expected, especially in long-term applications or under continuous high-stress operation. This subtle aging effect can be overlooked during initial testing but becomes evident after extended use. In some cases, learned behavior emerges from the interaction of transistor characteristics with the circuit’s power supply and ground noise. Voltage fluctuations, often caused by simultaneous switching of multiple gates (known as simultaneous switching noise), can temporarily pull the supply voltage down or cause ground shifts. This transient behavior can lead to some NAND gates misinterpreting input signals, resulting in unexpected outputs. Such phenomena highlight the importance of robust power distribution networks and careful circuit layout in integrated circuit design. In conclusion, while NAND gates are commonly viewed as straightforward digital components, their silicon-level behaviors are influenced by a myriad of subtle physical and electrical effects. Variations introduced during fabrication, leakage currents, parasitic elements, temperature fluctuations, aging, and power supply noise all contribute to differences in how individual gates perform. Recognizing and mitigating these effects require meticulous design, rigorous testing, and an understanding that the idealized symbol or truth table only tells part of the story. As electronic devices continue to shrink and operate at increasingly higher speeds, appreciating these nuanced behaviors becomes essential for reliable and precise circuit engineering.

Articles11 months ago

Intelligence on a Chip: The Evolution of Internal Logic in Microcontrollers

In the rapidly evolving world of technology, microcontrollers have become the silent workhorses powering everything from household appliances to advanced robotics. At the heart of their capabilities lies internal logic, an intricate web of circuitry that determines how these tiny devices interpret inputs and generate outputs. Over the decades, the evolution of this internal logic—from simple, hardwired circuits to sophisticated, programmable systems—has transformed what microcontrollers can accomplish, enabling unprecedented levels of automation, intelligence, and efficiency. Initially, microcontrollers were largely defined by their fixed-function logic, designed to perform specific tasks repeatedly. These early systems relied on AND, OR, and NOT gates arranged in simple combinational circuits, allowing them to execute a limited set of operations. The logic was hardwired; once fabricated, these circuits could not be altered or upgraded. This rigidity made early microcontrollers suitable for straightforward applications such as timer functions or basic control systems, but limited their flexibility in more complex scenarios. As digital design advanced, engineers began integrating more complex logical structures, including flip-flops, counters, and registers, enabling basic decision-making capabilities. The introduction of Read-Only Memory (ROM) and Programmable Read-Only Memory (PROM) allowed for some programmability, but often the internal logic remained somewhat static. To overcome these limitations, the development of microcontrollers with embedded Programmable Logic Devices (PLDs) and Field Programmable Gate Arrays (FPGAs) marked a significant turning point. These programmable logic elements allowed designers to customize internal logic post-fabrication, opening the door to more versatile and adaptable devices. The true transformation came with the advent of microcontrollers featuring integrated microprocessors and software programmability. Here, internal logic was no longer limited to fixed hardware; instead, it could be reconfigured through firmware updates. This shift toward software-defined logic enabled complex algorithms, digital signal processing, and even basic machine learning tasks within microcontrollers, fundamentally expanding their operational scope. Engineers could now optimize performance, improve security, and add new functionalities simply by updating software, reducing costs and development time. More recent advancements have seen the integration of System-on-Chip (SoC) architectures, combining multiple cores, specialized accelerators, and extensive memory within a single chip. This convergence affords microcontrollers with highly nuanced internal logic capable of handling real-time data processing, multimedia functions, and secure communications simultaneously. The internal logic circuitry in such devices is highly sophisticated, often involving multiple layers of hardware and software co-design that work seamlessly to deliver high performance with minimal power consumption. Furthermore, the rise of artificial intelligence at the edge has stimulated innovations in internal logic architectures. Contemporary microcontrollers incorporate dedicated AI accelerators and neural processing units, enabling smart features like voice recognition, image analysis, and predictive maintenance directly on devices with limited resources. The internal logic in these chips is tailored specifically for these tasks, combining hardware accelerators optimized for matrix operations and algorithms with the flexibility of traditional microcontroller features. In essence, the journey of internal logic in microcontrollers has been one of increasing complexity and adaptability. From fixed, hardwired circuits to dynamic, reprogrammable systems embedded with AI capabilities, each step has broadened the horizon for what microcontrollers can do. As technology continues to advance, the internal logic within these tiny devices will undoubtedly become even more sophisticated, enabling smarter, more connected, and more autonomous systems that seamlessly integrate into daily life. This ongoing evolution underscores the profound importance of internal logic design—transforming humble chips into the core brains of tomorrow’s digital ecosystems.

Articles11 months ago

How Oscillators Work in Modern Logic Circuits: From Quartz to FPGAs

Oscillators play a fundamental role in modern electronics, serving as the heartbeat of digital systems by generating precise timing signals that synchronize various components. Their operation, while seemingly straightforward, involves a complex interplay of physical phenomena and circuit design principles that ensure stable and accurate frequency generation. From the humble quartz crystal oscillators to the sophisticated programmable logic devices like Field Programmable Gate Arrays (FPGAs), understanding how oscillators work reveals much about the evolution and intricacies of electronic timing sources. Historically, quartz crystal oscillators have been the gold standard for frequency stability and accuracy. These devices exploit the piezoelectric effect, where certain materials generate an electric voltage in response to mechanical stress. When a quartz crystal is shaped into a resonant structure and integrated into an oscillator circuit, it acts as a highly stable resonator. When energized, it vibrates at its natural resonant frequency, which is determined by its physical dimensions and cut. The oscillator circuit amplifies these vibrations and feeds them back in a positive feedback loop, sustaining constant oscillations. This process demands a delicate balance: the circuit must provide enough gain to compensate for losses but must also include mechanisms—like automatic gain control—to prevent the oscillations from growing uncontrollably or damping out altogether. The result is a stable, precise frequency source that forms the backbone of clocks in computers, communication systems, and countless other electronic devices. As technology advanced, the limitations of quartz crystals—particularly their fixed frequency and susceptibility to environmental changes—prompted the development of more flexible oscillators. Voltage-controlled oscillators (VCOs), for example, allow their frequency to be tuned by an external voltage, making them essential in phase-locked loops (PLLs) used for frequency synthesis and stabilization. PLLs are active feedback systems that compare the phase of a generated signal to a reference, adjusting the VCO to lock onto the desired frequency. This arrangement enables complex frequency modulation, synchronization across devices, and noise filtering—crucial for modern communications and signal processing. In the realm of digital logic, especially with the advent of Field Programmable Gate Arrays (FPGAs), oscillators have taken on new forms. FPGAs often integrate their own clock management tiles, which include phase-locked loops and delay-locked loops, allowing for the generation of multiple synchronized clocks with variable frequencies. These programmable tools provide designers with the flexibility to create application-specific oscillators that can be adjusted dynamically to optimize performance, power consumption, or other parameters. Such integrated oscillators typically involve digital phase-locked loop architectures, where a digitally controlled oscillator (DCO) is synchronized to a reference clock. These DCOs utilize digital feedback algorithms and delay elements, making them adaptable and easier to integrate into complex digital systems. Another notable trend is the use of surface acoustic wave (SAW) and MEMS (Micro-Electro-Mechanical Systems) oscillators. These devices leverage mechanically resonant structures to achieve high frequency stability in compact, low-power packages. They're increasingly common in mobile devices and IoT gadgets, where size constraints and power efficiency are paramount. Their operation resembles that of quartz crystals but with the added advantage of easier integration into modern semiconductor fabrication processes. In essence, the evolution of oscillators reflects the broader trajectory of electronics: from rigid, specialized components to versatile, integrated solutions. While the fundamental principles—resonance and feedback—remain constant, the materials, design techniques, and applications have transformed dramatically. Today’s oscillators are not just simple frequency sources—they are sophisticated, adaptable components that underpin the entire fabric of modern digital systems, enabling everything from high-speed communications to real-time processing in complex FPGA-based architectures. This ongoing innovation ensures that as technology pushes forward, oscillators will continue to evolve, providing ever more precise, flexible, and efficient timing solutions for the future.

Articles11 months ago

Perfect Signals Don’t Exist: How Noise Shaping Drives the Future of Electronics

In the realm of electronics, the pursuit of perfection has often driven engineers and scientists to push the boundaries of what’s possible. For decades, the goal was simple: create signals that are as clean and error-free as possible, with minimal noise or distortion. But as technology has advanced and our devices have become more sophisticated, a new understanding has emerged. Perfect signals, it turns out, do not truly exist, and perhaps never will. Instead, the focus has shifted toward mastering the art of noise shaping, a technique that allows us to control and distribute unwanted noise in ways that enhance overall system performance. Noise shaping is a concept deeply rooted in the principles of signal processing, especially in analog-to-digital and digital-to-analog conversion. The idea is not to eliminate noise altogether—an impossible task—but to manipulate its spectral distribution so that it becomes less perceptible or less disruptive to the intended signal. Think of it like a finely tuned audio equalizer that pushes undesirable frequencies into regions where they are less noticeable, or into frequency bands that can be filtered out more easily. This strategic redistribution of noise allows electronic devices to perform at levels that were once considered unattainable, delivering clearer audio in smartphones, more accurate measurements in scientific instruments, and smoother data streams in high-speed communications. Modern noise shaping techniques have become foundational in many cutting-edge technologies. For instance, delta-sigma modulators, widely used in audio DACs (digital-to-analog converters), employ high-order noise shaping to push quantization noise out of the audible range. This process results in remarkably high-fidelity sound reproduction from relatively inexpensive components. Similarly, in data storage and transmission, noise shaping enhances the signal-to-noise ratio, enabling higher data rates and more reliable communications without requiring prohibitively expensive hardware. One of the most fascinating aspects of noise shaping is its philosophical shift away from perfection toward optimization. Instead of striving for absolutely pristine signals—which, due to physical limitations and quantum effects, is fundamentally impossible—researchers aim to make noise less intrusive and more manageable. This is where the concept of psychoacoustics becomes essential. By understanding how humans perceive sound, engineers can design noise shaping algorithms that mask or diminish noise in ways that are virtually imperceptible to the human ear. This synergy of human perception and engineering innovation has led to consumer electronics with audio quality that surpasses expectations, despite the underlying presence of noise. Furthermore, noise shaping contributes significantly to the ongoing miniaturization and efficiency of electronic components. As devices shrink and power constraints tighten, the ability to manage noise effectively ensures that performance does not suffer. For example, in RF (radio frequency) systems, noise shaping helps maintain signal integrity over long distances or in noisy environments, extending communication reach and reliability. It also plays a critical role in emerging fields like quantum computing and nanoscale electronics, where physical and quantum noise sources are inherently significant, demanding sophisticated approaches to noise management. Despite its many advantages, noise shaping is not without challenges. Designing high-order filters and modulators requires complex algorithms and extensive computational resources. Precision is key; even tiny deviations can lead to increased noise or signal distortion. Researchers continuously seek novel methods, such as machine learning-enhanced algorithms, to refine noise shaping techniques further. This ongoing innovation underscores a fundamental truth in electronics: perfection is a moving target, but mastery over imperfection—via noise shaping—is the path forward. In essence, the realization that perfect signals don’t exist has liberated the field of electronics from its impossible quest for flawlessness. Instead, it has opened the door to a more pragmatic and sophisticated approach—one that accepts, manages, and even leverages noise to improve device performance. Noise shaping exemplifies this mindset beautifully, transforming an unavoidable byproduct into a secret weapon for the future of technology. As researchers continue to explore and refine these methods, we can expect electronic systems that are more efficient, more resilient, and more in tune with the complex, imperfect world they inhabit. The future isn’t about eliminating noise entirely but about understanding and directing it—making noise shaping the cornerstone of next-generation electronics innovation.

Articles11 months ago

Why Some NAND Gates Behave Differently: Subtle Effects at the Silicon Level

NAND gates are fundamental building blocks in digital electronics, often regarded as the universal gate because of their ability to implement any logical function. Typically, their behavior is well-understood and predictable, derived from the principles of Boolean algebra and semiconductor physics. However, when delving into the silicon level, certain subtle effects can cause some NAND gates to behave unexpectedly or differently from their idealized models. These variations may surprise practitioners and can be critical considerations in high-precision or high-speed applications. At the most basic level, NAND gates are constructed from transistors—either MOSFETs in CMOS technology or BJTs in older designs. In CMOS structures, the gates involve a complementary pair of p-type and n-type MOSFETs. When the input signals change state, the current path through these transistors switches, producing the desired logic output. Ideally, this switching process occurs instantly; in practice, several subtle physical effects influence the actual timing, power consumption, and even the logic threshold levels. One factor leading to different behaviors is the variability inherent in silicon fabrication. Manufacturing processes can introduce tiny differences in transistor dimensions, doping concentrations, and oxide thicknesses, all of which influence the threshold voltage (Vth) of individual transistors. Such variations can cause some NAND gates to switch at slightly different input voltages or exhibit asymmetric rise and fall times, affecting circuit timing and potentially causing logic errors in tightly synchronized systems. Another subtle effect involves leakage currents. Although CMOS transistors are designed to minimize current flow when off, in reality, small leakage paths exist. These leakage currents are sensitive to temperature fluctuations, supply voltage variations, and manufacturing imperfections. In some cases, they can cause marginally different gate behaviors, especially at low supply voltages or very high speeds, where the leaky transistors might inadvertently switch states or delay switching. Parasitic capacitances and inductances also come into play at the silicon level. Even tiny parasitic elements associated with transistor junctions, interconnects, and the overall circuit layout can influence the speed and stability of NAND gates. These effects are often more pronounced at higher frequencies, where the inductive and capacitive elements introduce phase shifts and potential signal integrity issues, leading to behaviors deviating from the ideal digital switching profiles. Temperature effects are equally significant. As the chip heats up during operation, semiconductor properties shift—threshold voltages decrease or increase, carrier mobility changes, and leakage currents can spike. These shifts can temporarily alter the behavior of certain NAND gates, causing timing skew or voltage level variations. Such temperature-dependent behavior can be particularly problematic in environments with fluctuating conditions, like outdoor electronics or high-performance computing systems. Moreover, aging phenomena such as bias temperature instability (BTI) and hot-carrier injection gradually alter the transistor characteristics over time. These changes can lead to slow drifts in the threshold voltage, intermittently causing some NAND gates to behave differently than expected, especially in long-term applications or under continuous high-stress operation. This subtle aging effect can be overlooked during initial testing but becomes evident after extended use. In some cases, learned behavior emerges from the interaction of transistor characteristics with the circuit’s power supply and ground noise. Voltage fluctuations, often caused by simultaneous switching of multiple gates (known as simultaneous switching noise), can temporarily pull the supply voltage down or cause ground shifts. This transient behavior can lead to some NAND gates misinterpreting input signals, resulting in unexpected outputs. Such phenomena highlight the importance of robust power distribution networks and careful circuit layout in integrated circuit design. In conclusion, while NAND gates are commonly viewed as straightforward digital components, their silicon-level behaviors are influenced by a myriad of subtle physical and electrical effects. Variations introduced during fabrication, leakage currents, parasitic elements, temperature fluctuations, aging, and power supply noise all contribute to differences in how individual gates perform. Recognizing and mitigating these effects require meticulous design, rigorous testing, and an understanding that the idealized symbol or truth table only tells part of the story. As electronic devices continue to shrink and operate at increasingly higher speeds, appreciating these nuanced behaviors becomes essential for reliable and precise circuit engineering.

Articles11 months ago

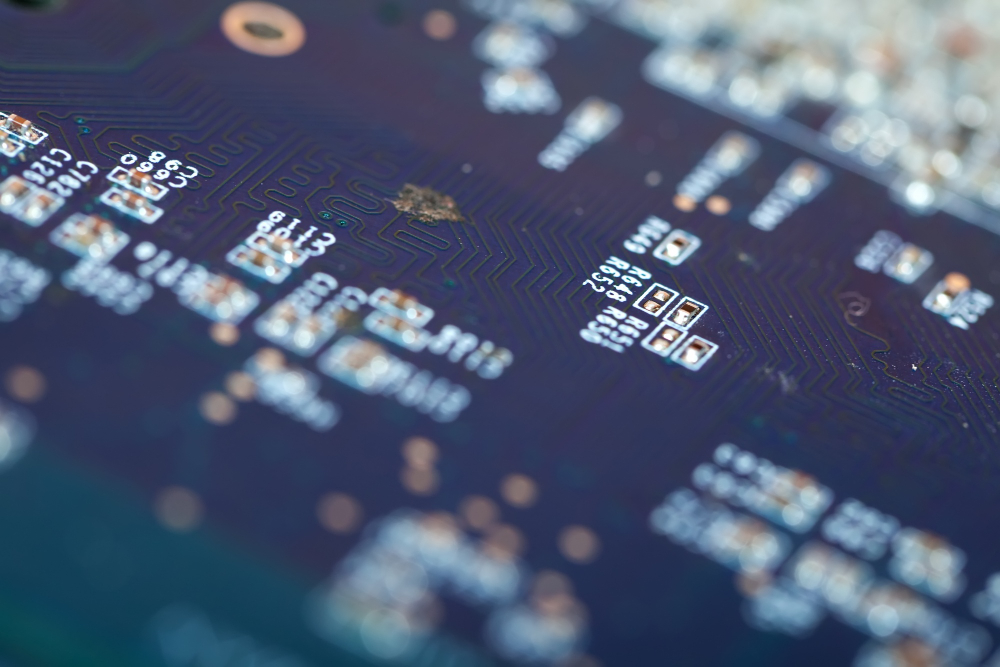

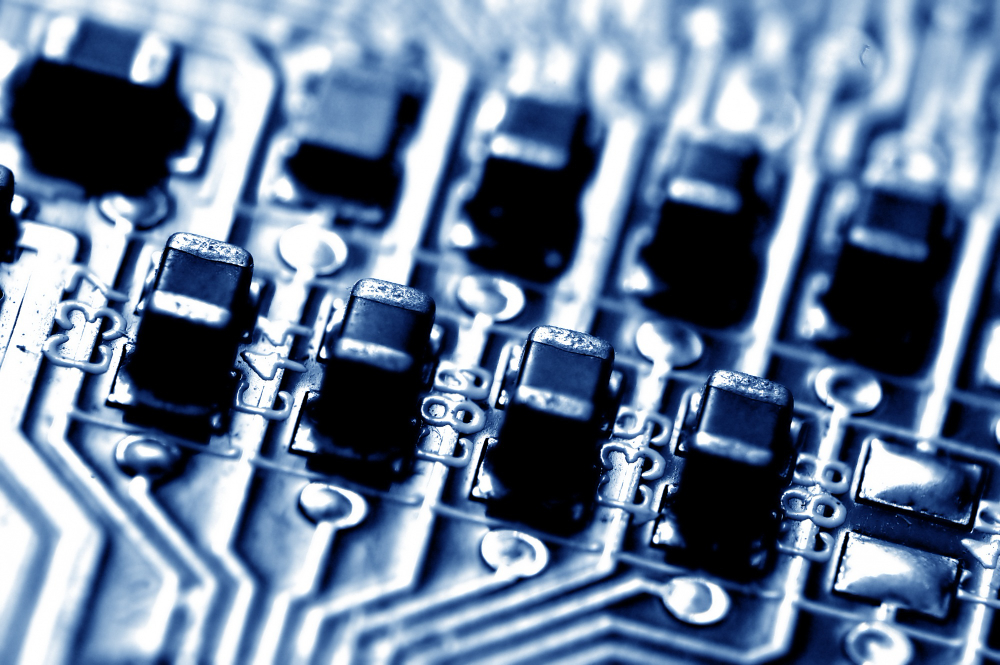

What Lies Beneath the Package: A Close Look Inside Modern Chips

In today's rapidly advancing technological landscape, microchips form the invisible backbone of virtually every device we rely on. From smartphones and laptops to autonomous vehicles and medical equipment, these tiny but mighty components power the modern world. Yet, behind their sleek exterior lies an intricate tapestry of engineering marvels, material science, and manufacturing precision that often goes unnoticed. Understanding what lies beneath the package of a modern chip reveals not just the complexity of these devices, but also the incredible sophistication that enables their functionality. At the heart of a typical semiconductor chip is the silicon wafer—a thin slice of high-purity silicon crystal that serves as the foundation for intricate circuitry. The process begins with photolithography, where ultraviolet light transfers microscopic patterns onto the wafer's surface, defining the pathways and components of the integrated circuit. This process, repeated multiple times with layers of conductive and insulating materials, results in the complex web of transistors, resistors, and capacitors that give the chip its processing power. Today’s chips contain billions of transistors, each just a few nanometers in size, packed together to perform millions of operations per second. These transistors act as tiny switches, switching on and off millions of times a second to execute computations. But what truly brings these circuits to life is the precise layering and doping processes that manipulate electrical properties at the microscopic level. Doping introduces impurities into silicon to enhance its conductivity, creating regions of positive or negative charge—p-type or n-type—crucial for forming the transistors' junctions. The result is a highly controlled environment where electron flow can be manipulated with extraordinary precision. This level of control is essential for the chip's efficiency, speed, and power consumption. Encasing these intricate circuits is the package—a protective shell that shields the fragile internal components from environmental damage, heat, and mechanical stress. Modern chip packages are marvels of engineering in their own right. They often comprise multiple layers, including a substrate, bonding wires, and a heat spreader. The substrate, usually made of ceramic or plastic, provides structural support and electrical connections, while bonding wires or solder bumps connect the internal silicon die to external circuitry. As devices have demanded higher performance and miniaturization, packaging technology has evolved to include ball grid arrays (BGAs) and flip-chip designs, which allow for a greater number of connections in a smaller footprint. One of the most critical aspects of modern chips is heat management. With billions of transistors operating simultaneously, thermal dissipation becomes an engineering challenge. Advanced cooling techniques, including heat sinks, vapor chambers, and even embedded microfluidic channels, are integrated within the packaging to maintain optimal operating temperatures. Without effective heat dissipation, chips risk overheating, which can lead to malfunction or reduced lifespan. Beyond the physical structures, the materials used in chip manufacturing continue to evolve. Researchers are exploring alternatives like graphene and transition metal dichalcogenides for future transistors, promising even smaller, faster, and more energy-efficient devices. Interconnects—a network of tiny copper or aluminum wires—are also being refined for lower resistance and higher data throughput, essential for keeping pace with growing data demands. The leap from basic microprocessors to today's advanced chips has been driven by innovations across multiple domains—material science, nanotechnology, and precision manufacturing. Each layer, each connection, and each minute element work together seamlessly, enabling the powerful computational capabilities we have come to depend on. Peering inside a modern chip reveals a marvel of engineering that marries the microscopic with the macro, turning what appears to be simple silicon into the engines of modern innovation. Understanding these inner workings not only sheds light on the marvels of tomorrow’s technology but also underscores the complexity and ingenuity behind the devices that have become integral to our daily lives.